Technical Document

Specifications

Brand

Texas InstrumentsLogic Function

Buffer

Output Type

Open Drain

Number of Elements per Chip

6

Maximum Propagation Delay Time @ Maximum CL

10.6 ns @ 3.3 V, 15.2 ns @ 2.5 V, 7.5 ns @ 5 V

Maximum High Level Output Current

-0.002mA

Maximum Low Level Output Current

16mA

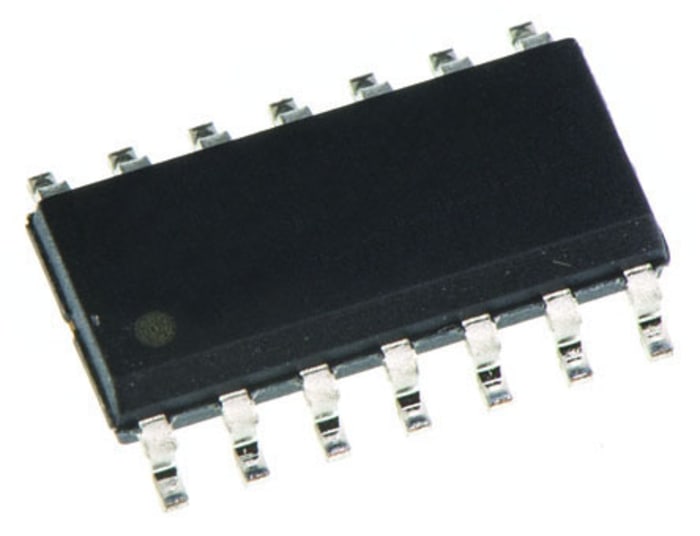

Mounting Type

Surface Mount

Package Type

SOIC

Pin Count

14

Logic Family

LV

Dimensions

8.65 x 3.91 x 1.58mm

Maximum Operating Supply Voltage

5.5 V

Height

1.58mm

Length

8.65mm

Width

3.91mm

Minimum Operating Supply Voltage

2 V

Minimum Operating Temperature

-40 °C

Propagation Delay Test Condition

50pF

Maximum Operating Temperature

+85 °C

Product details

74LV Family, Texas Instruments

Low-Voltage CMOS logic

Operating Voltage: 2 to 5.5

Compatibility: Input LVTTL/TTL, Output LVCMOS

74LV Family

Stock information temporarily unavailable.

€ 10.50

€ 1.05 Each (In a Pack of 10) (Exc. Vat)

€ 13.02

€ 1.302 Each (In a Pack of 10) (inc. VAT)

10

€ 10.50

€ 1.05 Each (In a Pack of 10) (Exc. Vat)

€ 13.02

€ 1.302 Each (In a Pack of 10) (inc. VAT)

Stock information temporarily unavailable.

10

| Quantity | Unit price | Per Pack |

|---|---|---|

| 10 - 40 | € 1.05 | € 10.50 |

| 50 - 90 | € 1.00 | € 10.00 |

| 100 - 240 | € 0.913 | € 9.13 |

| 250 - 490 | € 0.822 | € 8.22 |

| 500+ | € 0.781 | € 7.81 |

Technical Document

Specifications

Brand

Texas InstrumentsLogic Function

Buffer

Output Type

Open Drain

Number of Elements per Chip

6

Maximum Propagation Delay Time @ Maximum CL

10.6 ns @ 3.3 V, 15.2 ns @ 2.5 V, 7.5 ns @ 5 V

Maximum High Level Output Current

-0.002mA

Maximum Low Level Output Current

16mA

Mounting Type

Surface Mount

Package Type

SOIC

Pin Count

14

Logic Family

LV

Dimensions

8.65 x 3.91 x 1.58mm

Maximum Operating Supply Voltage

5.5 V

Height

1.58mm

Length

8.65mm

Width

3.91mm

Minimum Operating Supply Voltage

2 V

Minimum Operating Temperature

-40 °C

Propagation Delay Test Condition

50pF

Maximum Operating Temperature

+85 °C

Product details

74LV Family, Texas Instruments

Low-Voltage CMOS logic

Operating Voltage: 2 to 5.5

Compatibility: Input LVTTL/TTL, Output LVCMOS